CDK是以极简开发为理念打造的集成开发环境,全面接入云端开发资源,结合图形化调试分析工具,可大幅提升研发效率,非常适用于RISC-V MCU的应用开发。

近日,为了帮助客户将更多的精力投入到应用和业务逻辑相关的设计,更快地实现平台迁移,缩短产品上市时间,RISC-V MCU领军企业爱普特和阿里平头哥联手推出基于CDK的图形化配置。这是一套利用可扩展的标识语言和动态库来实现的配置系统,可以帮助客户用最简单的鼠标点选方式自动生成初始化配置函数。

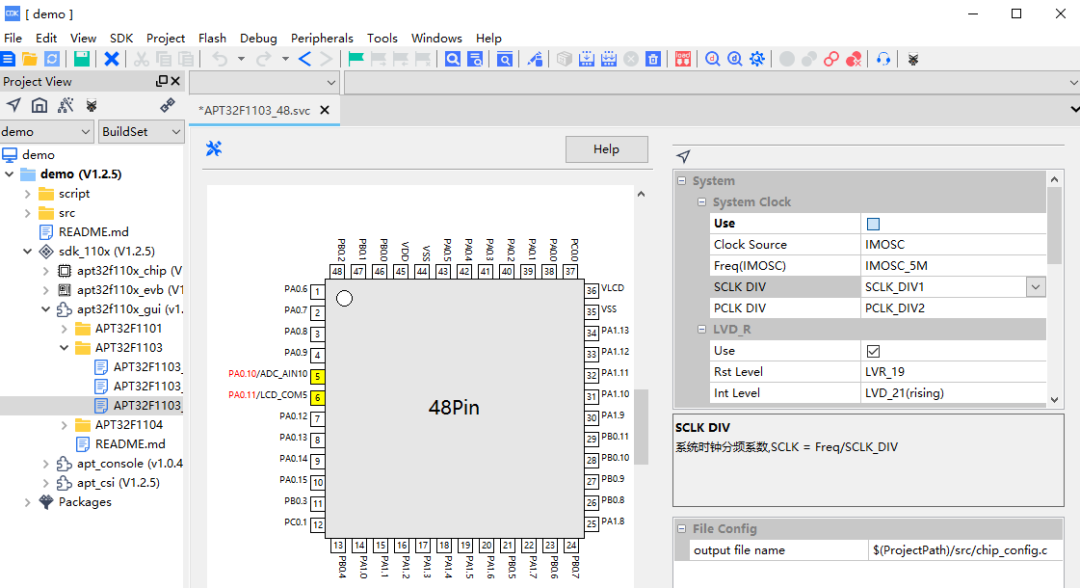

通过图形化配置,可以实现模块初始化。用户不再需要关注寄存器级的细节,只需要将注意力集中在参数选择上。其次,图形化配置界面中展示了每一款芯片相关功能支持的所有配置选项,并提供了对应的文本注释。客户可以一定程度地脱离产品使用手册,直接了解到对应产品相应的可配置内容,从而大幅缩短研发时间,加速产品落地。

爱普特及阿里平头哥已完成了使用率较高的配置项,方便广大工程师使用,并会陆续推出各个常用模块的初始化配置。

管脚配置

- 管脚AF功能配置

- 管脚上下拉配置

- 管脚(输出)监控配置

- 管脚(输出)驱动能力/斜率/恒流配置

- 管脚(输入)TTL配置

系统配置

- 系统时钟(包括PCLK)配置

- LVR/LVD配置

- IWDT配置

- SRAM check配置

- FLASH check配置

- CoreTick使用与否

EXI配置

- 管脚和group的对应关系:我们的芯片支持将同一个管脚上的外部信号接到不同的IO group上,形成不同的触发信号

- 触发模式选择

CDK使用界面

目前CDK图形化配置可支持爱普特多系列全国产高可靠MCU产品型号,如APT32F110X,APT32F171X,APT32F103X等。

作为阿里平头哥在MCU领域深度战略合作伙伴,爱普特与平头哥一直都致力于推动全国产MCU生态建设。目前,除了CDK的优化配置,爱普特和平头哥还正携手打造“1520”的生态标准,即1天上手、5天出原型,20天量产。

爱普特希望有越来越多的合作伙伴可以加入到RISC-V MCU生态建设中来,共同推动RISC-V 生态的蓬勃发展!